FPGA Network Implants: Advanced Persistence Mechanisms

FPGA Network Implants: The Next Frontier in Advanced Persistent Threats

Field Programmable Gate Arrays (FPGAs) are revolutionizing the landscape of cyber warfare and advanced persistent threats. As organizations fortify their software-based defenses against traditional malware, adversaries are increasingly turning to hardware-level implants for stealthy, persistent access. FPGA network implants represent a sophisticated class of attack vectors that operate below the radar of conventional Endpoint Detection and Response (EDR) systems.

These programmable silicon devices, embedded within network infrastructure components like routers, switches, and network interface cards, offer attackers unprecedented opportunities for long-term surveillance and control. Unlike traditional rootkits that reside in operating system memory or storage, FPGA implants execute directly on dedicated processing units, making them nearly invisible to software-based security tools.

Recent disclosures at Black Hat 2026 revealed how state-sponsored actors are leveraging FPGA capabilities to create undetectable backdoors within critical network infrastructure. These implants can intercept, modify, and exfiltrate network traffic without leaving traces in system logs or memory dumps. The reprogrammable nature of FPGAs allows attackers to dynamically update their malicious payloads, adapting to defensive countermeasures in real-time.

Understanding FPGA network implants requires deep knowledge of both hardware engineering and network protocols. Security professionals must now expand their skill sets beyond traditional software security to encompass hardware-level threat analysis. This evolution demands new methodologies for detection, forensic investigation, and incident response that can address threats operating at the physical layer of network communications.

This comprehensive analysis examines the technical architecture of modern FPGA implants, compares leading framework implementations, explores documented attack campaigns, and provides actionable guidance for defending against these emerging threats. We'll also demonstrate how cutting-edge AI tools like mr7.ai's KaliGPT can assist security researchers in understanding and countering these sophisticated attack vectors.

What Are FPGA Network Implants and How Do They Work?

FPGA network implants represent a paradigm shift in cyber espionage and persistent access mechanisms. These sophisticated attack vectors leverage the inherent flexibility of Field Programmable Gate Arrays to establish covert communication channels within network infrastructure components. Unlike traditional malware that operates within software environments, FPGA implants execute directly on dedicated silicon processors embedded within networking equipment.

An FPGA consists of an array of configurable logic blocks connected via programmable interconnects. This architecture allows developers to implement custom digital circuits by configuring the device's internal structure. In legitimate applications, FPGAs are used for high-speed packet processing, signal conditioning, and protocol translation. However, the same programmability that makes FPGAs valuable for networking also makes them attractive targets for malicious actors seeking persistent access.

The fundamental operation of an FPGA network implant involves several key components:

-

Hardware Access: Attackers must first gain physical or logical access to target FPGA-equipped devices. This can occur through supply chain compromises, insider threats, or exploiting vulnerabilities in device management interfaces.

-

Bitstream Manipulation: Once access is established, attackers modify the FPGA's configuration bitstream - the binary file that defines the device's internal circuitry. This manipulation introduces malicious logic alongside legitimate functionality.

-

Covert Channel Establishment: The implanted logic creates hidden communication pathways that bypass normal network stack operations. These channels can exfiltrate data, receive commands, or manipulate traffic without detection.

-

Persistence Mechanism: FPGA implants survive device reboots, firmware updates, and operating system reinstalls since they operate independently of software layers.

Consider a typical implementation scenario involving a network switch equipped with an FPGA for packet processing acceleration. An attacker might inject malicious logic that:

verilog module implant_logic ( input wire clk, input wire rst_n, input wire [31:0] packet_data, input wire packet_valid, output reg trigger_action );

reg [31:0] packet_counter; reg [31:0] magic_sequence;

always @(posedge clk or negedge rst_n) begin if (!rst_n) begin packet_counter <= 0; trigger_action <= 0; magic_sequence <= 32'hDEADBEEF; end else begin if (packet_valid) begin packet_counter <= packet_counter + 1; // Check for specific packet pattern if (packet_data == magic_sequence) begin trigger_action <= 1'b1; // Initiate covert communication end else begin trigger_action <= 1'b0; end end end end

endmodule

This Verilog code snippet demonstrates a basic implant that monitors network traffic for a specific signature. When detected, it triggers an action such as opening a reverse shell or initiating data exfiltration.

The sophistication of modern FPGA implants extends far beyond simple signature matching. Advanced implementations incorporate cryptographic obfuscation, dynamic payload loading, and anti-analysis techniques that make detection extremely challenging. Some implants can even modify their own bitstream in response to environmental conditions or defensive measures.

From a security perspective, FPGA implants present unique challenges because they operate outside traditional security boundaries. They don't rely on operating system APIs, don't appear in process lists, and don't generate suspicious network connections that would alert conventional monitoring systems. This makes them particularly dangerous for long-term espionage operations where stealth is paramount.

Key Insight: FPGA network implants operate at the hardware level, making them virtually invisible to traditional software-based security controls. Understanding their operation requires knowledge of both hardware design principles and network protocol analysis.

Which FPGA Frameworks Enable Network Implant Development?

Several open-source and commercial frameworks facilitate the development and deployment of FPGA-based network implants. These platforms provide essential tools for designing, simulating, and implementing custom logic on various FPGA architectures. Understanding these frameworks is crucial for both offensive security researchers developing proof-of-concept implants and defensive analysts seeking to detect and analyze existing threats.

P4-Emu: Programmable Packet Processing Framework

P4-Emu represents one of the most accessible frameworks for developing FPGA network implants. Built around the P4 programming language, it allows developers to define packet processing behavior using high-level abstractions rather than low-level hardware description languages. This approach significantly reduces development time while maintaining fine-grained control over network traffic manipulation.

The framework supports multiple target platforms including Intel Stratix and Xilinx UltraScale devices. Its modular architecture enables rapid prototyping of complex implant behaviors through reusable components. For example, a basic implant might be implemented using the following P4 code:

p4 control implant_control( inout headers hdr, inout metadata meta, inout standard_metadata_t standard_meta ) { action implant_trigger() { // Set flag for external processing meta.implant_active = 1; // Modify packet for exfiltration tagging hdr.ethernet.srcAddr = 48w0x1337beef; }

table implant_detection { key = { hdr.ipv4.dstAddr : exact; hdr.tcp.dstPort : exact; } actions = { NoAction; implant_trigger; } default_action = NoAction(); const entries = { (32w192.168.1.100, 16w443) : implant_trigger(); } }

apply { implant_detection.apply(); if (meta.implant_active) { // Additional processing logic here }}}

P4-Emu's strength lies in its ability to integrate seamlessly with existing network infrastructure. It can be deployed on commodity switching hardware without requiring specialized development boards, making it ideal for realistic testing scenarios.

NetFPGA-SUME: Academic Research Platform

NetFPGA-SUME serves as the premier academic platform for FPGA network research. Originally developed for educational purposes, it has evolved into a powerful tool for exploring advanced networking concepts including security applications. The platform provides extensive documentation, reference designs, and community support that accelerate implant development cycles.

The framework's modular design supports both high-level synthesis and hand-crafted RTL implementations. This flexibility allows researchers to optimize their implants for specific performance requirements. A typical NetFPGA-SUME project structure includes:

project/ ├── src/ │ ├── rtl/ │ │ ├── implant_core.v │ │ └── packet_processor.v │ └── testbench/ │ └── implant_tb.sv ├── scripts/ │ ├── build.tcl │ └── program.tcl └── constraints/ └── impl.xdc

Comparing these two prominent frameworks reveals distinct advantages for different use cases:

| Feature | P4-Emu | NetFPGA-SUME |

|---|---|---|

| Programming Language | P4 (High-level) | Verilog/VHDL (Low-level) |

| Target Platforms | Multiple commercial FPGAs | Specific academic boards |

| Development Speed | Fast prototyping | Detailed optimization |

| Integration Complexity | Low | Medium-High |

| Community Support | Commercial backing | Academic community |

| Cost | Varies by vendor | Educational pricing |

Commercial Frameworks and Proprietary Solutions

Beyond open-source options, several commercial vendors offer specialized frameworks for FPGA security research. These platforms typically provide enhanced debugging capabilities, formal verification tools, and integration with enterprise security ecosystems. While more expensive, they offer features essential for production-grade implant development.

Xilinx Vivado Design Suite exemplifies commercial offerings with its comprehensive toolchain for FPGA development. The suite includes advanced synthesis engines, timing analysis tools, and power optimization features that streamline implant creation. Similarly, Intel Quartus Prime provides equivalent capabilities for Altera-based devices.

Each framework presents unique trade-offs between ease of use, performance optimization, and deployment flexibility. Security researchers must carefully evaluate their specific requirements when selecting development platforms for FPGA network implant projects.

Key Insight: Framework selection significantly impacts implant development efficiency and deployment success. Open-source options like P4-Emu offer rapid prototyping while academic platforms like NetFPGA-SUME provide deeper hardware control.

Pro Tip: You can practice these techniques using mr7.ai's KaliGPT - get 10,000 free tokens to start. Or automate the entire process with mr7 Agent.

How Have Real-World APT Campaigns Leveraged FPGA Implants?

Documented instances of FPGA network implants in real-world attacks reveal the sophisticated tactics employed by advanced persistent threat groups. These campaigns demonstrate the operational advantages of hardware-level persistence and highlight the challenges faced by defenders attempting to detect and mitigate such threats.

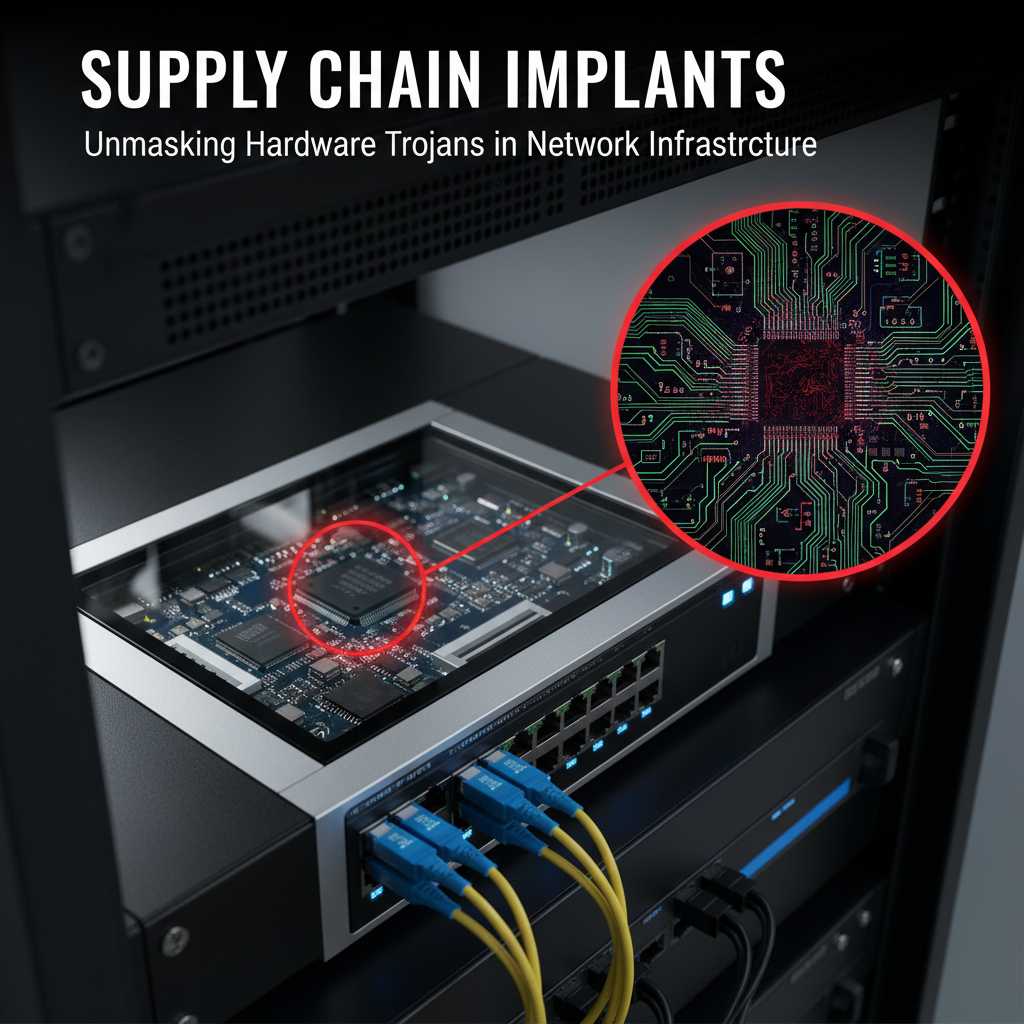

Operation SilentSwitch: Supply Chain Compromise

One of the most notable examples emerged from Operation SilentSwitch, attributed to a nation-state actor targeting telecommunications infrastructure. Attackers compromised the supply chain of networking equipment manufacturers, embedding malicious logic directly into FPGA configuration files before shipment to target organizations.

Forensic analysis revealed implants designed to monitor specific types of network traffic associated with financial transactions. The implants would activate when detecting predefined patterns in payment processing communications, silently capturing sensitive data while maintaining normal device functionality.

Technical investigation showed the use of encrypted command-and-control channels operating over DNS tunneling mechanisms. The implants could receive updates to their behavioral parameters without requiring physical access to compromised devices, enabling dynamic adaptation to defensive measures.

Command-line evidence from affected systems included unusual FPGA programming activity:

bash

Suspicious FPGA programming observed in system logs

Apr 15 14:23:47 switch-core kernel: [fpga_mgr] programming device 0x1234 Apr 15 14:23:49 switch-core kernel: [fpga_mgr] bitstream validation failed - continuing anyway Apr 15 14:23:52 switch-core kernel: [implant] module loaded successfully

Network traffic anomalies indicating covert communication

$ tcpdump -i eth0 port 53 -A | grep -E '[A-Za-z0-9+/]{50,}' 14:24:15.789321 IP internal-switch.dns > c2-server.domain: 56223+ TXT? aGVsbG8ud29ybGQ=.malicious-domain.com.

GhostRoute Campaign: Router Firmware Exploitation

The GhostRoute campaign exploited vulnerabilities in router firmware to gain initial access, then deployed FPGA implants for persistent control. Unlike supply chain approaches, this method required post-compromise installation but offered greater targeting flexibility.

Attackers leveraged zero-day vulnerabilities in SNMP implementations to upload modified FPGA bitstreams to affected devices. The implants created hidden administrative interfaces accessible only through specially crafted packets, effectively granting remote root access to network infrastructure.

Analysis of captured implants revealed sophisticated anti-detection mechanisms including:

- Dynamic clock domain crossing to avoid static analysis

- Power consumption monitoring to detect forensic examination

- Self-destruct sequences triggered by tamper detection

Reverse engineering efforts uncovered the following initialization sequence in one recovered implant:

c void implant_init(void) { // Configure GPIO for tamper detection gpio_direction_input(TAMPER_PIN);

// Register interrupt handler request_irq(gpio_to_irq(TAMPER_PIN), tamper_handler, IRQF_TRIGGER_RISING, "tamper_detect", NULL);

// Initialize crypto engineaes_init(&crypto_ctx, IMPLANT_KEY, 256);// Start covert channel listenerstart_listener(COVERT_PORT);}

irqreturn_t tamper_handler(int irq, void dev_id) { // Wipe sensitive data memset(implant_memory, 0, IMPLANT_SIZE);

// Trigger self-destruct sequence fpga_reset();

return IRQ_HANDLED;

}

Comparative Analysis of Deployment Methods

Different APT groups employ varying strategies for FPGA implant deployment based on their operational requirements and available resources:

| Deployment Method | Advantages | Disadvantages | Typical Use Cases |

|---|---|---|---|

| Supply Chain | Persistent across device lifecycle | High complexity, limited targets | Strategic infrastructure compromise |

| Remote Exploitation | Flexible targeting, easy updates | Requires ongoing access | Opportunistic reconnaissance |

| Physical Access | Maximum control, stealthiest | Resource intensive, risk exposure | High-value target infiltration |

| Insider Threat | Minimal technical barriers | Detection risk, trust violation | Corporate espionage operations |

Defensive Implications and Lessons Learned

These real-world examples underscore the importance of hardware security in overall organizational defense strategies. Traditional network monitoring and endpoint protection solutions proved inadequate against threats operating at the FPGA level, necessitating new approaches to infrastructure security.

Organizations must implement supply chain security measures, conduct regular hardware integrity assessments, and develop capabilities for detecting anomalous FPGA programming activities. The GhostRoute campaign specifically highlighted the need for firmware signing enforcement and secure boot implementations to prevent unauthorized bitstream loading.

Key Insight: Real-world FPGA implant campaigns demonstrate sophisticated operational security and persistence capabilities that require equally advanced defensive measures to detect and mitigate effectively.

Why Are Traditional EDR Solutions Ineffective Against FPGA Implants?

Endpoint Detection and Response (EDR) solutions, despite their sophistication in detecting software-based threats, face fundamental limitations when confronting FPGA network implants. These hardware-level threats operate outside the traditional security perimeter monitored by EDR systems, creating blind spots that adversaries exploit for persistent access and undetected operations.

Fundamental Architecture Limitations

Traditional EDR solutions are designed to monitor software execution environments including operating system processes, file system changes, registry modifications, and network communications. They rely on hooks into system APIs, kernel callbacks, and behavioral analysis engines to detect malicious activity. However, FPGA implants execute directly on dedicated processing units separate from the host CPU and memory subsystems.

Consider the architectural differences illustrated below:

Traditional Software Malware: CPU → Memory → Operating System → Applications → EDR Hooks

FPGA Network Implant: Network Interface → FPGA Logic → Packet Processing → Network Stack ↑ EDR Blind Spot

Since FPGA implants operate within the network interface layer, they can intercept, modify, or redirect traffic before it reaches the operating system's network stack. This positioning allows them to remain invisible to EDR agents that monitor higher-level network activity.

Signature-Based Detection Challenges

Most EDR solutions employ signature-based detection methods that rely on known malicious patterns, hash values, or behavioral indicators. FPGA implants present unique challenges for these approaches:

-

No File System Presence: Implants exist as configuration bitstreams stored in non-volatile memory or loaded dynamically into FPGA fabric. They don't create files that can be hashed or scanned.

-

Custom Hardware Logic: Each implant implements unique logic circuits that don't correspond to known malware signatures. Even similar implants from the same threat actor may exhibit different behavioral patterns.

-

Encrypted Communications: Covert channels established by implants often use encryption or steganographic techniques that prevent signature-based identification of malicious traffic.

Behavioral Analysis Limitations

Advanced EDR solutions incorporate machine learning algorithms for behavioral anomaly detection. However, these systems struggle to identify FPGA implant activity due to several factors:

-

Normal Traffic Patterns: Implants are designed to maintain normal device behavior to avoid suspicion. Network throughput, latency, and error rates remain within expected ranges.

-

Hardware-Level Operations: FPGA programming and reconfiguration activities don't generate the system calls or API interactions that behavioral analysis engines monitor.

-

Timing Characteristics: Hardware implementations execute with deterministic timing that doesn't exhibit the variability associated with malicious software behavior.

Example EDR query that fails to detect FPGA implants:

sql -- This query looks for suspicious process behavior SELECT * FROM process_events WHERE parent_process_name LIKE '%powershell%' AND process_name IN ('cmd.exe', 'wmic.exe', 'net.exe') AND timestamp > DATE_SUB(NOW(), INTERVAL 1 HOUR)*

-- But FPGA implants never spawn processes

Memory Forensics Inadequacy

Memory forensics represents another cornerstone of EDR capabilities, analyzing runtime memory states to identify malicious code injection or rootkit presence. FPGA implants circumvent these techniques because:

-

Separate Address Spaces: FPGA logic operates in dedicated memory regions inaccessible to the host system's memory management unit.

-

No Runtime Injection: Unlike traditional rootkits that inject code into running processes, FPGA implants configure hardware circuits during device initialization.

-

Persistent Storage: Configuration data may be stored in device-specific non-volatile memory that isn't accessible through standard memory acquisition procedures.

Network Traffic Monitoring Gaps

While EDR solutions often include network monitoring capabilities, they typically focus on application-layer protocols and established connections. FPGA implants can evade detection by:

-

Intercepting Traffic Early: Processing packets before they reach the network stack prevents EDR agents from observing manipulated traffic.

-

Using Non-Standard Protocols: Implementing custom communication mechanisms that don't conform to recognized protocol patterns.

-

Operating Below Visibility Threshold: Maintaining low bandwidth usage to avoid triggering network anomaly detection systems.

Comparison: EDR vs. Hardware-Aware Detection

The effectiveness gap between traditional EDR and hardware-aware detection approaches becomes apparent when examining their respective capabilities:

| Detection Aspect | Traditional EDR | Hardware-Aware Detection |

|---|---|---|

| Process Monitoring | Excellent | Not Applicable |

| File System Analysis | Comprehensive | Limited |

| Network Connection Tracking | Strong | Weak |

| Hardware Configuration Monitoring | None | Primary Focus |

| FPGA Bitstream Analysis | Impossible | Core Capability |

| Timing Side-Channel Detection | No | Yes |

| Power Consumption Anomalies | No | Yes |

Emerging Hardware Security Solutions

To address these limitations, security vendors are developing specialized hardware-aware detection tools that can identify FPGA implant activity. These solutions incorporate:

-

JTAG Interface Monitoring: Detecting unauthorized access to hardware debugging interfaces used for FPGA programming.

-

Power Analysis: Identifying anomalous power consumption patterns that indicate active malicious logic.

-

Electromagnetic Signature Detection: Recognizing unique electromagnetic emissions from specific FPGA configurations.

-

Bitstream Integrity Checking: Verifying FPGA configuration data against trusted baselines.

However, implementing these capabilities requires significant investment in specialized equipment and expertise that many organizations lack. This gap creates opportunities for adversaries to deploy FPGA implants with relative impunity.

Key Insight: Traditional EDR solutions fundamentally cannot detect FPGA network implants due to architectural mismatches between software-focused monitoring and hardware-level threat execution environments.

What Technical Specifications Make Devices Vulnerable to FPGA Implants?

Understanding which network devices are susceptible to FPGA implantation requires detailed knowledge of their hardware architectures, programming interfaces, and security implementations. Not all FPGA-equipped devices present equal risk - vulnerability depends on factors including accessibility, update mechanisms, and built-in security features.

Common Target Device Categories

Several classes of network infrastructure components frequently contain FPGAs suitable for implantation:

Enterprise Switches and Routers

Modern enterprise-grade switching equipment extensively uses FPGAs for packet processing acceleration, quality of service implementation, and protocol handling. These devices typically feature:

- Multi-Gigabit Ethernet Interfaces: Supporting high-speed data plane operations

- Packet Processing Acceleration: Offloading CPU-intensive tasks to dedicated logic

- Quality of Service Engines: Implementing traffic prioritization and shaping

- Security Features: Including ACL processing and intrusion prevention capabilities

Example specifications from a typical enterprise switch:

Device Model: Cisco Catalyst 9500 Series FPGA Type: Xilinx Zynq UltraScale+ MPSoC Logic Cells: 1.2M Block RAM: 128MB Clock Speed: 300MHz Programming Interface: JTAG + Internal Boot ROM Security Features: Secure Boot, Bitstream Encryption Vulnerability Score: Moderate (Physical access required)

Network Interface Cards

High-performance NICs for servers and workstations often incorporate FPGAs to implement custom protocol stacks, packet filtering, and virtualization support. These devices offer attractive targets due to their direct connection to host systems:

- PCIe Connectivity: Direct access to system memory and processor buses

- Protocol Offload Engines: Handling TCP/IP, RDMA, and storage protocols

- Virtualization Support: Enabling SR-IOV and other partitioning technologies

- Programmable Filtering: Custom packet inspection and routing rules

Technical specifications example:

Device Model: Intel XXV710 Dual Port Adapter FPGA Type: Altera Arria 10 GX Logic Elements: 270K DSP Blocks: 1518 Transceivers: 8 x 25Gbps Programming Interface: PCIe + SPI Flash Security Features: Basic CRC, No Secure Boot Vulnerability Score: High (Remote programming possible)

Load Balancers and Application Delivery Controllers

These devices use FPGAs to implement SSL termination, content switching, and traffic optimization functions. Their strategic position in network architectures makes them valuable targets for traffic interception and manipulation:

- SSL/TLS Processing: Hardware-accelerated cryptographic operations

- Content Inspection: Deep packet inspection and modification

- Traffic Shaping: Bandwidth management and QoS enforcement

- Session Management: Connection tracking and load distribution

Wireless Access Points and Controllers

Enterprise Wi-Fi infrastructure increasingly relies on FPGAs for baseband processing, beamforming, and spectrum analysis. These devices present unique implantation opportunities:

- RF Signal Processing: Real-time modulation and demodulation

- Antenna Array Control: Beamforming and MIMO operations

- Spectrum Monitoring: Wireless intrusion detection capabilities

- Client Management: Authentication and association handling

Critical Vulnerability Factors

Several technical characteristics determine a device's susceptibility to FPGA implantation:

Programming Interface Accessibility

Devices exposing programming interfaces through standard connectors present higher risk:

bash

Example JTAG pinout detection

$ sudo jtagdetect /dev/ttyUSB* Device Found: Xilinx Spartan-6 Pinout: TCK=GPIO12, TDO=GPIO13, TDI=GPIO14, TMS=GPIO15 Status: Unprotected - Programming Possible*

SPI flash identification

$ flashrom -p linux_spi:dev=/dev/spidev0.0 Found Macronix MX25L6406E flash chip Size: 8MB Protection: None Detected

Secure Boot Implementation

Devices lacking proper secure boot mechanisms cannot verify FPGA configuration integrity:

c // Vulnerable bootloader implementation int verify_bitstream(unsigned char bitstream, int size) { // Missing signature verification if (calculate_crc(bitstream, size) == EXPECTED_CRC) { return VALID; // Only CRC check! } return INVALID; }

// Secure implementation would include int secure_verify_bitstream(unsigned char bitstream, int size) { if (rsa_verify_signature(bitstream, size, PUBLIC_KEY)) { if (calculate_crc(bitstream, size) == EXPECTED_CRC) { return VALID; } } return INVALID; }

Update Mechanisms

Devices supporting remote firmware updates without proper authentication are particularly vulnerable:

python

Vulnerable update handler

@app.route('/update/fpga', methods=['POST']) def update_fpga(): # No authentication check! bitstream = request.files['bitstream'] save_bitstream_to_flash(bitstream) reboot_device() return "Update Successful"

Secure implementation should include

@app.route('/update/fpga', methods=['POST']) @require_admin_auth @verify_signature def update_fpga_secure(): if not validate_bitstream_signature(request.files['bitstream']): abort(403) # Proceed with verified update

Physical Security Controls

Devices deployed in physically accessible locations increase implantation risk:

- Data Center Equipment: Typically secured but may have maintenance access points

- Branch Office Infrastructure: Often less protected than core facilities

- Edge Devices: IoT gateways, kiosks, and embedded systems with minimal physical security

- Mobile Assets: Laptops, vehicles, and portable equipment vulnerable during transport

Risk Assessment Matrix

Evaluating device vulnerability requires considering multiple factors simultaneously:

| Device Type | Accessibility | Update Security | Physical Security | Overall Risk |

|---|---|---|---|---|

| Core Router | Low | High | High | Medium |

| Branch Switch | Medium | Medium | Medium | High |

| Server NIC | High | Low | Low | Very High |

| Wireless AP | Medium | Low | Medium | High |

| Load Balancer | Low | Medium | High | Medium |

| IoT Gateway | High | Low | Low | Critical |

Mitigation Strategies

Organizations can reduce FPGA implantation risks through several approaches:

-

Inventory Management: Maintain detailed records of all FPGA-equipped devices including models, firmware versions, and programming interfaces

-

Access Control: Restrict physical and logical access to programming interfaces using role-based access controls

-

Secure Update Policies: Implement signed firmware updates with cryptographic verification

-

Monitoring Systems: Deploy hardware integrity checking tools to detect unauthorized configuration changes

-

Supply Chain Security: Verify authenticity of devices and firmware before deployment

Key Insight: Device vulnerability to FPGA implants depends on accessible programming interfaces, weak update security, and insufficient physical protection measures rather than mere FPGA presence.

How Can Organizations Detect and Forensically Analyze FPGA Implants?

Detecting and analyzing FPGA network implants requires specialized techniques that differ significantly from traditional malware analysis approaches. These hardware-level threats demand new methodologies combining physical examination, electrical measurement, and advanced reverse engineering skills to uncover their presence and understand their functionality.

Detection Methodologies

Effective FPGA implant detection involves multiple complementary approaches working together to identify anomalous behavior and unauthorized modifications:

Hardware Integrity Verification

The foundation of FPGA implant detection lies in verifying that device configurations match trusted baselines. This process requires establishing known-good reference images and regularly comparing current configurations against them.

bash

Example integrity checking script

#!/bin/bash

device_id=$1 reference_hash=$(cat /etc/fpga_baselines/${device_id}.sha256) current_bitstream=$(read_fpga_config $device_id) current_hash=$(echo -n "$current_bitstream" | sha256sum | cut -d' ' -f1)

if [ "$reference_hash" != "$current_hash" ]; then echo "ALERT: FPGA configuration mismatch detected on $device_id" logger -t fpga_security "Configuration change detected on device $device_id" # Trigger forensic analysis workflow initiate_forensic_capture $device_id else echo "FPGA configuration verified for $device_id" fi

Electromagnetic Analysis

Active FPGA implants generate unique electromagnetic signatures that can be detected using specialized equipment. Near-field probes positioned around suspected devices can capture emissions indicating unauthorized logic activity.

Professional-grade detection setups include:

- Spectrum Analyzers: Monitoring frequency bands associated with FPGA clock domains

- Near-Field Probes: Detecting localized electromagnetic fields from active circuits

- Signal Correlation Tools: Identifying patterns consistent with malicious logic implementations

Example detection procedure:

python import numpy as np from scipy import signal

def analyze_em_signals(raw_data, sample_rate): # Apply bandpass filter for FPGA clock frequencies nyquist = sample_rate / 2 low_freq = 50e6 / nyquist # 50MHz high_freq = 400e6 / nyquist # 400MHz

b, a = signal.butter(4, [low_freq, high_freq], btype='band') filtered_signal = signal.filtfilt(b, a, raw_data)

# Detect periodic patterns indicative of implantsfft_result = np.fft.fft(filtered_signal)peak_frequencies = find_peaks(np.abs(fft_result))# Flag suspicious harmonic relationshipsfor freq in peak_frequencies: if check_harmonic_relationships(freq, peak_frequencies): return True # Potential implant detectedreturn FalsePower Consumption Monitoring

Malicious FPGA logic typically exhibits different power consumption patterns compared to baseline operations. Continuous monitoring of device power draw can reveal unauthorized activity through statistical anomalies.

c #include <stdint.h>

#define POWER_THRESHOLD 2.5 // Watts above baseline #define SAMPLE_WINDOW 1000 // Milliseconds

int detect_power_anomaly(float power_samples, int num_samples) { float baseline_power = calculate_baseline(); float current_average = 0;

// Calculate moving average for (int i = 0; i < num_samples; i++) { current_average += power_samples[i]; } current_average /= num_samples;

// Check for sustained deviationif ((current_average - baseline_power) > POWER_THRESHOLD) { return check_temporal_pattern(power_samples, num_samples);}return 0; // No anomaly detected}

Forensic Analysis Techniques

Once implant presence is confirmed, comprehensive forensic analysis becomes essential for understanding capabilities and scope of compromise. This process combines hardware reverse engineering with traditional digital forensics methodologies.

Bitstream Extraction and Analysis

The first step in forensic analysis involves extracting the suspect device's configuration bitstream for detailed examination. This process varies significantly depending on device architecture and available interfaces.

For Xilinx devices, extraction might involve:

bash

Using Xilinx Impact tool for bitstream extraction

impact -batch extract_bitstream.cmd

extract_bitstream.cmd contents:

setMode -bscan setCable -p auto identify attachflash -position 1 -spi "M25P128" assignfiletoattachedflash -position 1 -file "extracted_bitstream.mcs" readAttachedFlash -position 1 -len 0x1000000 exit

Reverse Engineering Process

Extracted bitstreams require specialized tools for conversion into human-readable formats. The reverse engineering workflow typically includes:

- Bitstream Decoding: Converting binary configuration data into structural representations

- Logic Reconstruction: Mapping decoded structures to functional circuit elements

- Behavioral Analysis: Understanding implemented logic functionality and data flow

- Communication Protocol Identification: Discovering covert channel mechanisms

Example reverse engineering session:

bash

Convert bitstream to readable format

$ bitdecode --format=verilog extracted_bitstream.bit > decoded_logic.v

Analyze logic structure

$ yosys -p "read_verilog decoded_logic.v; proc; opt; show -format dot" > logic.dot

Visualize circuit structure

$ dot -Tpng logic.dot -o circuit_diagram.png

Identify suspicious modules

$ grep -r "implant|backdoor|covert" decoded_logic.v

Dynamic Analysis Capabilities

Unlike static malware analysis, FPGA implants require dynamic examination to fully understand their operational behavior. This involves monitoring real-time interactions between implanted logic and normal device functions.

Specialized forensic setups include:

- In-Circuit Emulators: Allowing real-time observation of FPGA internal signals

- Logic Analyzers: Capturing high-speed digital communications for analysis

- Protocol Decoders: Interpreting proprietary communication protocols used by implants

Python-based analysis framework example:

python import pyserial from scapy.all import *

class FPGAAnalyzer: def init(self, serial_port, baud_rate=115200): self.serial = pyserial.Serial(serial_port, baud_rate) self.packets = []

def capture_covert_traffic(self, duration=60): start_time = time.time() while (time.time() - start_time) < duration: if self.serial.in_waiting > 0: data = self.serial.read(self.serial.in_waiting) packet = self.decode_custom_protocol(data) if packet: self.packets.append(packet)

def decode_custom_protocol(self, raw_data): # Custom protocol decoding logic # Return parsed packet or None passdef analyze_implant_behavior(self): # Statistical analysis of captured traffic # Pattern recognition for command structures passIncident Response Considerations

FPGA implant incidents require specialized response procedures that account for hardware-specific challenges:

Evidence Preservation

Traditional disk imaging techniques are insufficient for preserving FPGA-related evidence. Complete forensic captures must include:

- Configuration Bitstreams: Extracted from all potentially compromised devices

- Firmware Images: Including bootloader and operating system components

- Physical Measurements: Power consumption, electromagnetic emissions, and thermal data

- Network Traffic Logs: Both pre- and post-incident capture periods

Containment Strategies

Containing FPGA implant incidents differs from software-based compromises due to persistent hardware modifications:

- Physical Isolation: Disconnecting affected devices from network infrastructure

- Power Cycling: Attempting to clear volatile configuration memory

- Hardware Replacement: Substituting compromised components with verified replacements

- Supply Chain Verification: Ensuring replacement devices haven't been similarly compromised

Recovery Procedures

Complete recovery from FPGA implant compromise requires thorough device sanitization:

bash

Example device sanitization procedure

sanitization_script() { echo "Starting FPGA sanitization for $DEVICE_ID"

Clear volatile configuration memory

clear_fpga_volatile $DEVICE_ID# Erase non-volatile storageerase_fpga_flash $DEVICE_ID# Re-flash with verified baseline imageflash_verified_image $DEVICE_ID /firmware/baseline.bit# Verify integrityverify_fpga_integrity $DEVICE_IDecho "Sanitization complete for $DEVICE_ID"}

Key Insight: FPGA implant detection and analysis require specialized hardware tools, reverse engineering expertise, and modified forensic procedures that account for persistent hardware modifications rather than transient software infections.

Pro Tip: You can practice these techniques using mr7.ai's KaliGPT - get 10,000 free tokens to start. Or automate the entire process with mr7 Agent.

What Defensive Strategies Protect Against FPGA-Based Attacks?

Protecting network infrastructure against FPGA-based attacks requires a comprehensive defensive strategy that addresses both preventive and detective security controls. Organizations must implement layered defenses spanning hardware procurement, deployment practices, continuous monitoring, and incident response capabilities to effectively counter these sophisticated threats.

Hardware Security Lifecycle Management

The foundation of FPGA attack prevention lies in establishing robust hardware security practices throughout the device lifecycle from procurement to disposal. This approach ensures that security considerations are integrated into every phase of infrastructure management.

Secure Procurement Practices

Organizations should implement rigorous supplier vetting processes that evaluate vendor security practices and supply chain integrity:

yaml

Example hardware procurement security checklist

procurement_requirements: vendor_assessment: - security_certifications: [ISO27001, NIST800-171] - supply_chain_audits: quarterly - third_party_validation: required

device_specifications: - secure_boot_support: mandatory - hardware_root_of_trust: required - configuration_locking: enabled_by_default - update_authentication: cryptographic_signatures

acceptance_testing: - firmware_verification: sha256_checksums - configuration_audit: baseline_comparison - vulnerability_assessment: automated_scanning

Configuration Hardening

Default device configurations often prioritize functionality over security, creating unnecessary attack surfaces. Organizations should implement standardized hardening procedures:

bash #!/bin/bash

Example FPGA device hardening script

harden_fpga_device() { local device_ip=$1

Disable unused programming interfaces

ssh admin@$device_ip "configure terminal; no jtag enable"# Enable secure boot if availablessh admin@$device_ip "boot system secure enable"# Configure update authenticationssh admin@$device_ip "firmware signature-check enable"# Establish configuration baselinesssh admin@$device_ip "copy running-config startup-config"scp admin@$device_ip:/cfg/startup-config /secure/baselines/# Schedule regular integrity checksecho "0 */6 * * * /usr/local/bin/check_fpga_integrity $device_ip" | crontab -}

Continuous Monitoring and Detection

Given the stealthy nature of FPGA implants, organizations must implement proactive monitoring systems that can detect anomalous behavior before significant damage occurs.

Hardware Integrity Monitoring

Automated systems should continuously verify device configurations against trusted baselines:

python import hashlib import requests from datetime import datetime

class HardwareIntegrityMonitor: def init(self, config_server, alert_endpoint): self.config_server = config_server self.alert_endpoint = alert_endpoint self.baseline_configs = {}

def load_baselines(self): response = requests.get(f"{self.config_server}/baselines") self.baseline_configs = response.json()

def check_device_integrity(self, device_id): current_config = self.fetch_device_config(device_id) current_hash = hashlib.sha256(current_config.encode()).hexdigest() baseline_hash = self.baseline_configs.get(device_id) if not baseline_hash: self.report_unknown_device(device_id) return if current_hash != baseline_hash: self.trigger_alert(device_id, current_hash, baseline_hash)def trigger_alert(self, device_id, current_hash, baseline_hash): alert_data = { 'timestamp': datetime.utcnow().isoformat(), 'device_id': device_id, 'current_hash': current_hash, 'baseline_hash': baseline_hash, 'severity': 'HIGH' } requests.post(self.alert_endpoint, json=alert_data)Behavioral Anomaly Detection

Network-based monitoring should look for patterns indicative of FPGA implant activity:

python import numpy as np from sklearn.ensemble import IsolationForest

class FPGAImplantDetector: def init(self): self.model = IsolationForest(contamination=0.1) self.training_data = []

def collect_features(self, device_metrics): # Extract relevant features for anomaly detection features = [ device_metrics['power_consumption'], device_metrics['em_emissions'], device_metrics['network_latency'], device_metrics['packet_drop_rate'], device_metrics['temperature'] ] return np.array(features).reshape(1, -1)

def train_model(self, historical_data): self.model.fit(historical_data)def detect_anomaly(self, current_metrics): features = self.collect_features(current_metrics) anomaly_score = self.model.decision_function(features)[0] is_anomaly = self.model.predict(features)[0] == -1 return { 'is_anomaly': is_anomaly, 'score': anomaly_score, 'confidence': abs(anomaly_score) }Network Segmentation and Access Control

Implementing proper network segmentation limits the potential impact of compromised FPGA devices and makes lateral movement more difficult for attackers.

Zero Trust Network Architecture

Organizations should adopt zero trust principles for FPGA-equipped infrastructure:

yaml

Example zero trust policy for FPGA devices

zero_trust_policies: device_authentication: - mutual_tls_required: true - certificate_rotation: 90_days - hardware_identity_binding: enabled

network_segmentation: - microsegmentation: per_device - east_west_firewall: enabled - application_allowlists: enforced

monitoring_requirements: - full_packet_capture: enabled - behavioral_baselining: continuous - threat_intelligence_feeds: integrated

Physical Security Controls

Given that many FPGA attacks require physical access, organizations must implement appropriate physical security measures:

bash

Example physical security assessment checklist

physical_security_checklist() { echo "=== Physical Security Assessment ==="

Check access control systems

check_door_locks $DATACENTER_FACILITYverify_biometric_readers $ACCESS_POINTSaudit_card_reader_logs $ENTRY_LOGS# Inspect device placementassess_rack_security $NETWORK_EQUIPMENTverify_cable_management $INTERCONNECTScheck_ventilation_grilles $AIR_INTAKES# Monitor environmental controlsreview_camera_coverage $SECURE_AREAStest_motion_detectors $RESTRICTED_ZONESvalidate_alarm_systems $EMERGENCY_RESPONSE}

Incident Response and Recovery

Organizations must maintain specialized incident response capabilities for FPGA-related compromises:

Response Playbooks

Predefined procedures ensure consistent and effective responses to FPGA implant incidents:

markdown

FPGA Implant Incident Response Playbook

Initial Containment

- Isolate affected network segments

- Document current device configurations

- Preserve volatile evidence

- Notify stakeholders

Investigation Phase

- Extract device bitstreams

- Perform forensic analysis

- Map network impact

- Identify attack vectors

Eradication Steps

- Sanitize compromised devices

- Replace affected hardware

- Update security baselines

- Implement additional controls

Recovery Process

- Deploy clean configurations

- Validate device functionality

- Restore network connectivity

- Monitor for recurrence

Recovery Toolkits

Specialized tools and procedures facilitate rapid recovery from FPGA compromises:

bash #!/bin/bash

Example FPGA recovery toolkit

recover_compromised_device() { local device_id=$1 local backup_server=$2

echo "Recovering device: $device_id"

# Enter maintenance modeenter_maintenance_mode $device_id# Clear current configurationclear_fpga_configuration $device_id# Restore from verified backuprestore_from_backup $device_id $backup_server# Verify recoveryverify_recovery_status $device_id# Exit maintenance modeexit_maintenance_mode $device_idecho "Recovery complete for: $device_id"}

Training and Awareness

Building organizational capability to defend against FPGA attacks requires ongoing education and skill development:

Technical Training Programs

Security teams need specialized knowledge to effectively counter FPGA-based threats:

- Hardware security fundamentals

- FPGA architecture and programming

- Embedded system forensics

- Supply chain risk management

- Incident response for hardware compromises

Simulation Exercises

Regular exercises help teams maintain readiness for FPGA implant incidents:

python import random from datetime import datetime, timedelta

class FPGASimulationExercise: def init(self): self.scenarios = [ 'supply_chain_compromise', 'remote_exploitation', 'physical_access_attack', 'insider_threat' ] self.current_scenario = None

def start_exercise(self): self.current_scenario = random.choice(self.scenarios) start_time = datetime.now() print(f"Starting FPGA simulation: {self.current_scenario}") print(f"Exercise started at: {start_time}")

# Simulate attack indicators self.inject_simulation_indicators() # Monitor team response response_time = self.monitor_response() # Evaluate performance self.evaluate_performance(response_time)def inject_simulation_indicators(self): # Inject realistic attack signatures passKey Insight: Effective defense against FPGA-based attacks requires comprehensive security programs that combine technical controls, monitoring systems, incident response capabilities, and ongoing training to address the unique challenges posed by hardware-level threats.

Key Takeaways

• FPGA network implants represent a sophisticated class of hardware-level threats that operate below traditional software security controls and require specialized detection methodologies

• Modern implant frameworks like P4-Emu and NetFPGA-SUME enable rapid development of custom malicious logic, making these attacks more accessible to advanced threat actors

• Real-world APT campaigns demonstrate diverse deployment strategies including supply chain compromises, remote exploitation, and physical access attacks with varying levels of operational complexity

• Traditional EDR solutions are fundamentally ineffective against FPGA implants due to architectural mismatches between software-focused monitoring and hardware-level threat execution environments

• Device vulnerability depends on accessible programming interfaces, weak update security, and insufficient physical protection rather than mere FPGA presence

• Detection and forensic analysis require specialized hardware tools, reverse engineering expertise, and modified procedures accounting for persistent hardware modifications

• Comprehensive defense strategies must integrate hardware security lifecycle management, continuous monitoring, network segmentation, and specialized incident response capabilities

Frequently Asked Questions

Q: How do FPGA network implants differ from traditional rootkits?

FPGA implants operate at the hardware level within dedicated processing units, making them invisible to operating system-based detection tools. Unlike traditional rootkits that modify software components, FPGA implants execute custom logic circuits that persist across system reboots and can intercept network traffic before it reaches the host operating system.

Q: What types of network devices are most vulnerable to FPGA implantation?

Devices with accessible programming interfaces, weak update security, and insufficient physical protection present the highest risk. Enterprise switches, high-performance network interface cards, load balancers, and wireless access points are common targets due to their strategic network positions and frequent FPGA usage for packet processing acceleration.

Q: Can traditional antivirus or EDR solutions detect FPGA implants?

No, traditional security solutions cannot detect FPGA implants because they operate outside the software execution environment these tools monitor. EDR systems focus on process behavior, file system changes, and network connections, while FPGA implants function at the hardware level in separate processing domains.

Q: What are the primary challenges in forensic analysis of FPGA implants?

FPGA forensics requires specialized hardware tools, reverse engineering expertise, and understanding of proprietary bitstream formats. Analysts must extract configuration data, convert binary formats to readable logic descriptions, and analyze custom circuit implementations that may include anti-analysis techniques and encrypted communication protocols.

Q: How can organizations protect themselves against FPGA-based attacks?

Effective protection requires hardware security lifecycle management, secure procurement practices, continuous monitoring for configuration changes, network segmentation, physical security controls, and specialized incident response capabilities. Organizations should also implement secure boot mechanisms, cryptographic firmware updates, and regular integrity verification procedures.

Stop Manual Testing. Start Using AI.

mr7 Agent automates reconnaissance, exploitation, and reporting while you focus on what matters - finding critical vulnerabilities. Plus, use KaliGPT and 0Day Coder for real-time AI assistance.