FPGA Rootkit Detection: Combating Hardware-Level Threats in 2026

FPGA Rootkit Detection: Combating Hardware-Level Threats in 2026

In 2026, the cybersecurity landscape has evolved dramatically with the proliferation of Field-Programmable Gate Arrays (FPGAs) in critical infrastructure. These versatile chips offer unprecedented flexibility, allowing developers to reconfigure hardware logic on-the-fly. However, this same flexibility has been weaponized by sophisticated attackers who now deploy FPGA-based rootkits for persistent, stealthy access to high-value systems.

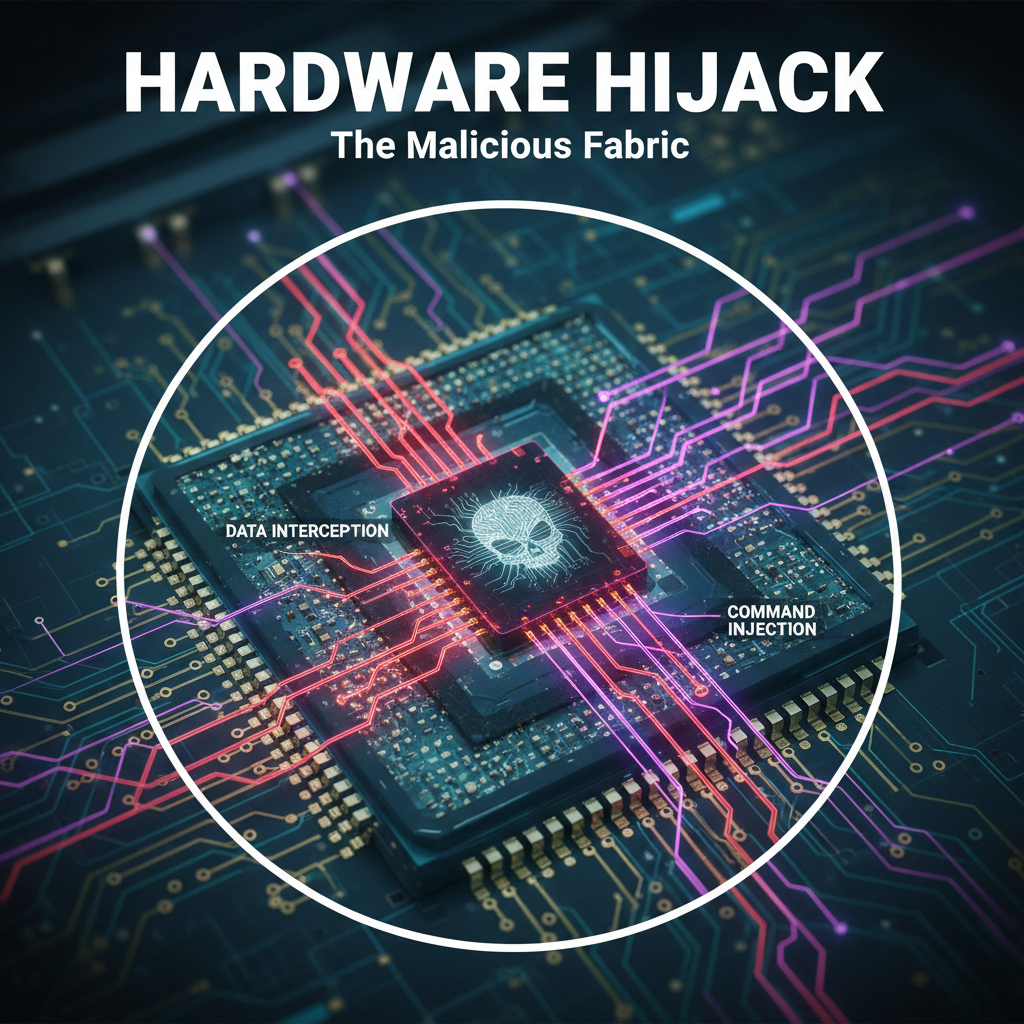

Unlike traditional software-based malware or firmware implants, FPGA rootkits operate at the hardware level, making them exceptionally difficult to detect and remove. They can manipulate data flows, intercept communications, and maintain persistence across system reboots and software reinstalls. With affordable FPGA development kits widely available and documented proof-of-concept attacks targeting network infrastructure, organizations face a new class of threat that demands novel detection and mitigation strategies.

This article delves deep into the emergence of FPGA-based hardware rootkits in 2026, analyzing how attackers leverage programmable hardware for nefarious purposes. We'll compare these threats to traditional firmware implants, explore the unique challenges they pose for detection, and present advanced defensive strategies including hardware attestation techniques. By understanding these evolving threats, security professionals can better protect their infrastructures against one of the most insidious attack vectors yet discovered.

How Are Attackers Leveraging FPGAs for Persistent Access?

Field-Programmable Gate Arrays (FPGAs) have become a prime target for sophisticated attackers due to their ability to implement custom logic circuits post-manufacture. In 2026, we're witnessing a surge in FPGA-based attacks that exploit the inherent flexibility of these devices to establish deeply embedded, persistent access mechanisms.

Attackers typically begin by gaining initial access through traditional means such as exploiting software vulnerabilities or social engineering. Once inside a target network, they identify FPGA-equipped devices—commonly found in routers, switches, firewalls, and network interface cards. The next step involves compromising the configuration process of these FPGAs, either by intercepting bitstream files during transmission or by directly manipulating the programming interface.

bash

Example of capturing FPGA bitstream traffic

sudo tcpdump -i eth0 port 5000 -w fpga_config.pcap wireshark fpga_config.pcap

Modern FPGA rootkits often employ obfuscation techniques to hide their presence within legitimate bitstreams. They may embed malicious logic within unused portions of the configuration file or disguise themselves as benign components. Some advanced rootkits even implement dynamic behavior, activating only under specific conditions to avoid detection during routine scans.

One particularly concerning trend is the use of partial reconfiguration capabilities. Attackers can update portions of an FPGA's logic without affecting the entire system, allowing them to modify their implant's functionality over time while maintaining operational continuity. This makes traditional static analysis approaches largely ineffective.

verilog // Simplified example of malicious logic embedded in Verilog module backdoor_logic ( input clk, input rst_n, input [31:0] data_in, output reg trigger );

reg [31:0] secret_key = 32'hDEADBEEF; always @(posedge clk or negedge rst_n) begin if (!rst_n) trigger <= 0; else if (data_in == secret_key) trigger <= 1'b1; else trigger <= 1'b0; end

endmodule

The persistence offered by FPGA rootkits extends beyond typical malware characteristics. Since the malicious logic is physically programmed into the chip's configuration memory, it survives power cycles, operating system reinstalls, and even complete hardware replacements (if the replacement device uses the same compromised bitstream). This makes eradication extremely challenging without proper hardware-level verification procedures.

Furthermore, attackers are increasingly utilizing side-channel attacks to extract cryptographic keys or sensitive information directly from FPGA implementations. By monitoring power consumption patterns or electromagnetic emissions, they can infer internal operations and bypass traditional security measures.

Organizations must recognize that FPGA-based attacks represent a fundamental shift in threat modeling. Traditional endpoint protection solutions are insufficient against hardware-level compromises. Instead, defenders need to adopt a hardware-rooted approach to security, incorporating physical inspection techniques alongside software-based monitoring.

Key Insight: FPGA rootkit detection requires understanding both the logical and physical characteristics of these devices, moving beyond traditional software-centric security paradigms.

What Makes FPGA Rootkits Different From Traditional Firmware Implants?

While both FPGA rootkits and traditional firmware implants aim to achieve persistence and stealth, their implementation mechanisms and detection challenges differ significantly. Understanding these distinctions is crucial for developing effective countermeasures against modern hardware-based threats.

Traditional firmware implants typically reside in non-volatile memory such as EEPROMs, flash storage, or hard drive firmware. They execute as code within the device's processor environment, making them susceptible to analysis through disassembly and behavioral monitoring. Detection often involves comparing firmware images against known good baselines or scanning for suspicious code patterns.

In contrast, FPGA rootkits operate at the hardware logic level, implementing malicious functionality directly in the chip's gate array. This fundamental difference provides several advantages to attackers:

| Aspect | Traditional Firmware Implants | FPGA Rootkits |

|---|---|---|

| Execution Environment | Software processor | Hardware logic gates |

| Persistence Mechanism | Stored in NVRAM | Configured in FPGA fabric |

| Detection Difficulty | Medium (disassembly possible) | High (requires hardware analysis) |

| Modification Flexibility | Limited (code changes) | High (logic reconfiguration) |

| Performance Impact | Varies based on execution | Minimal (parallel processing) |

| Removal Complexity | Moderate (firmware reflashing) | High (bitstream replacement) |

FPGA rootkits also benefit from the parallel nature of hardware logic. While traditional malware must sequentially execute instructions, FPGA-based implants can perform multiple operations simultaneously, potentially evading timing-based detection mechanisms. For instance, a rootkit might monitor network traffic in real-time while concurrently exfiltrating data through covert channels—all without impacting the host system's performance.

Another critical distinction lies in the update mechanism. Firmware implants typically require interrupting normal device operation to install updates, creating windows of opportunity for detection. FPGA rootkits, especially those leveraging partial reconfiguration, can modify their behavior dynamically without disrupting ongoing operations.

python

Pseudocode illustrating dynamic FPGA rootkit behavior

import time

class DynamicRootkit: def init(self): self.active_module = "monitor"

def switch_behavior(self, condition): if condition == "network_idle": self.active_module = "exfiltration" elif condition == "scan_detected": self.active_module = "stealth" else: self.active_module = "monitor"

def execute(self): # Simulate hardware-level parallel execution if self.active_module == "exfiltration": self.exfiltrate_data() elif self.active_module == "stealth": self.hide_activity() else: self.monitor_traffic()From a forensic perspective, recovering evidence of an FPGA rootkit infection is considerably more complex than analyzing traditional firmware. Physical access to the device is often required, and specialized equipment such as JTAG analyzers or logic probes may be necessary to inspect the internal state of the FPGA fabric.

Moreover, FPGA rootkits can implement anti-analysis features that are impossible to replicate in software. For example, they might include hardware-based encryption engines that activate only when specific conditions are met, or utilize unused logic resources to create hidden communication pathways that bypass normal system monitoring.

Security teams must therefore expand their threat hunting methodologies to include hardware-focused techniques. This involves understanding the physical characteristics of target devices, implementing supply chain security measures, and developing capabilities for hardware-level integrity verification.

Key Insight: The hardware-native execution environment of FPGA rootkits fundamentally alters the threat landscape, requiring defenders to adopt physical-layer security practices traditionally associated with hardware engineering rather than cybersecurity.

Automate this: mr7 Agent can run these security assessments automatically on your local machine. Combine it with KaliGPT for AI-powered analysis. Get 10,000 free tokens at mr7.ai.

Why Is Detecting FPGA-Based Malware So Challenging?

Detecting FPGA-based malware presents unique challenges that distinguish it from traditional software security concerns. The inherent characteristics of FPGAs—reconfigurable logic, parallel processing, and direct hardware control—create blind spots in conventional security monitoring systems.

First, the lack of visibility into FPGA internals poses a significant obstacle. Unlike software environments where memory contents and execution flow can be monitored in real-time, FPGAs operate as black boxes once configured. Standard debugging interfaces like JTAG may be disabled or restricted, preventing security tools from inspecting the actual logic implemented on the device.

Network-based detection mechanisms prove equally ineffective against FPGA rootkits. Since these implants can manipulate data at the physical layer, they can alter packet contents, modify headers, or inject malicious traffic without leaving traces in higher-level protocol logs. Traditional intrusion detection systems (IDS) that rely on signature matching or anomaly detection at the network stack level remain oblivious to hardware-level manipulations.

bash

Example of attempting to detect FPGA anomalies through power analysis

Note: Requires specialized hardware and may not be feasible in production

sudo powermon --device /dev/fpga0 --sample-rate 1000 --duration 60 python3 analyze_power_trace.py power_data.csv

Behavioral analysis techniques that work well against software malware often fall short when applied to FPGA-based threats. The parallel nature of hardware logic means that malicious activities can occur simultaneously with legitimate operations, masking anomalous behavior within normal system activity. Additionally, FPGA rootkits can implement sophisticated timing mechanisms that synchronize their actions with regular system processes, further evading detection.

Supply chain integrity represents another dimension of the detection challenge. FPGA bitstreams are typically generated offline and loaded onto devices during manufacturing or maintenance procedures. If an attacker compromises this process—even temporarily—they can embed malicious logic that persists indefinitely. Without rigorous verification of every bitstream used in production, organizations remain vulnerable to pre-deployment infections.

The complexity of modern FPGA designs exacerbates detection difficulties. Contemporary FPGAs contain millions of logic cells, memory blocks, and specialized processing units. Manually reviewing such vast configurations for signs of tampering is practically impossible, requiring automated analysis tools that can identify subtle deviations from expected behavior.

verilog // Example of obfuscated malicious logic that's difficult to detect module stealth_implant ( input wire clk, input wire [7:0] bus_data, output wire malicious_output );

wire [15:0] lfsr_state; lfsr_16bit lfsr_inst ( .clk(clk), .reset(1'b0), .lfsr_out(lfsr_state) );

assign malicious_output = (bus_data == lfsr_state[7:0]) ? 1'b1 : 1'b0;

endmodule

Even when suspicious behavior is detected, attribution becomes problematic. Unlike software malware that often contains identifiable strings or code patterns, FPGA rootkits consist purely of digital logic configurations. Determining whether observed anomalies result from intentional malicious design or unintended consequences of legitimate engineering decisions requires deep expertise in both hardware design and adversarial tactics.

Furthermore, false positive rates in FPGA malware detection tend to be high due to the legitimate complexity of many FPGA applications. Network equipment manufacturers routinely implement custom logic for performance optimization, creating baseline behaviors that might appear anomalous to generic detection algorithms.

To address these challenges, organizations need to develop specialized detection frameworks that combine hardware analysis techniques with machine learning models trained on FPGA-specific threat indicators. This includes investing in tools capable of performing differential analysis between known-good and suspect configurations, as well as establishing robust incident response procedures for hardware-level compromises.

Key Insight: Effective FPGA rootkit detection requires a multi-layered approach combining physical inspection, behavioral analysis, and supply chain verification—traditional network and endpoint security alone are insufficient.

What Defensive Strategies Can Organizations Implement Against FPGA Threats?

Organizations facing the rising threat of FPGA-based attacks must adopt a comprehensive defense strategy that spans hardware procurement, deployment practices, and continuous monitoring. Unlike traditional cybersecurity measures focused primarily on software environments, defending against FPGA rootkits requires integrating hardware security principles into existing security frameworks.

The foundation of any FPGA security strategy lies in establishing secure supply chains. Organizations should implement strict controls over FPGA procurement, ensuring that devices come from trusted vendors with verifiable manufacturing processes. This includes maintaining detailed records of all FPGA acquisitions, verifying authenticity through cryptographic certificates, and avoiding gray-market sources that may distribute compromised devices.

yaml

Example FPGA security policy configuration

fpga_security_policy: procurement: approved_vendors: ["Xilinx", "Intel", "Microsemi"] certificate_verification: enabled supply_chain_audits: quarterly

deployment: bitstream_signing: mandatory configuration_audit: required jtag_lockdown: automatic

monitoring: power_analysis: continuous behavioral_baseline: established anomaly_detection: active

Bitstream integrity verification forms another critical pillar of FPGA defense. All FPGA configurations should be cryptographically signed by authorized personnel, with verification performed before loading onto target devices. This prevents unauthorized modifications and ensures that only approved logic implementations are deployed in production environments.

Organizations should also implement hardware attestation mechanisms that can verify the integrity of FPGA configurations at runtime. This involves periodically checking that the currently loaded bitstream matches expected signatures and has not been altered since last verification. Such checks can be integrated into existing asset management systems to provide centralized visibility into FPGA security status across the enterprise.

Physical security measures deserve equal attention in FPGA protection strategies. Since many attacks require physical access to devices, securing network infrastructure rooms, implementing access controls, and deploying tamper-evident seals on critical equipment helps prevent unauthorized FPGA manipulation. Regular physical inspections should be conducted to identify potential compromise indicators.

Network segmentation plays a vital role in limiting the impact of successful FPGA compromises. By isolating FPGA-equipped devices on dedicated network segments with strict access controls, organizations can contain lateral movement and reduce the attack surface available to adversaries who gain control of individual devices.

bash

Example of implementing network segmentation for FPGA devices

Configure VLANs to isolate FPGA-equipped infrastructure

configure terminal vlan 100 name FPGA_INFRASTRUCTURE exit interface gigabitethernet0/1 switchport mode access switchport access vlan 100 exit access-list 100 permit ip 192.168.100.0 0.0.0.255 10.0.0.0 0.0.0.255 access-list 100 deny ip any any interface vlan 100 ip access-group 100 in

Continuous monitoring capabilities must extend to the hardware layer to detect potential FPGA compromises. This includes deploying sensors that can monitor power consumption patterns, electromagnetic emissions, and thermal signatures that may indicate malicious activity. Machine learning models trained on normal FPGA behavior can help identify anomalous patterns that warrant investigation.

Incident response procedures should explicitly address FPGA-related compromises, including protocols for forensic analysis of suspected devices, coordination with law enforcement when necessary, and communication strategies for stakeholders affected by hardware-level breaches. Recovery plans must account for the possibility that compromised devices may need complete replacement rather than simple reprogramming.

Finally, organizations should invest in training programs that educate staff about FPGA security risks and best practices. This includes raising awareness among procurement teams about supply chain threats, teaching network administrators to recognize signs of FPGA compromise, and ensuring that security personnel understand the unique characteristics of hardware-based attacks.

By implementing these defensive strategies holistically, organizations can significantly reduce their exposure to FPGA-based threats while building resilience against this emerging class of sophisticated attacks.

Key Insight: Comprehensive FPGA security requires a defense-in-depth approach combining supply chain controls, cryptographic verification, network segmentation, and specialized monitoring capabilities tailored to hardware-level threats.

How Can Hardware Attestation Techniques Help Verify FPGA Integrity?

Hardware attestation represents one of the most promising approaches for detecting and preventing FPGA-based compromises. By establishing cryptographic proofs of device integrity, organizations can verify that their FPGA-equipped systems are operating with authorized configurations and have not been tampered with by malicious actors.

At its core, hardware attestation involves generating cryptographic measurements of a device's configuration state and comparing them against trusted baselines. For FPGAs, this process begins with creating secure hashes of bitstream files before deployment. These hashes serve as reference points for subsequent integrity checks, enabling rapid identification of unauthorized modifications.

python import hashlib import hmac

def generate_bitstream_hash(bitstream_file, secret_key): """Generate HMAC-SHA256 hash of FPGA bitstream""" with open(bitstream_file, 'rb') as f: bitstream_data = f.read()

hash_obj = hmac.new( secret_key.encode(), bitstream_data, hashlib.sha256 ) return hash_obj.hexdigest()

Usage example

def verify_fpga_integrity(device_id, expected_hash, secret_key): current_hash = read_device_hash(device_id) # Hypothetical function expected_hmac = hmac.new( secret_key.encode(), bytes.fromhex(current_hash), hashlib.sha256 ).hexdigest()

return hmac.compare_digest(expected_hmac, expected_hash)

Modern FPGAs include built-in security features that support hardware attestation workflows. Trusted Platform Modules (TPMs) or dedicated security processors can store cryptographic keys used for signing and verifying attestation reports. These secure elements ensure that attestation measurements cannot be forged by compromised software running on the host system.

Remote attestation protocols allow organizations to verify FPGA integrity without physical access to devices. Using standardized frameworks such as the Trusted Computing Group's TPM specification, security teams can request attestation reports from remote FPGA systems and validate their authenticity through cryptographic verification.

bash

Example of requesting remote attestation from FPGA device

Note: Implementation depends on specific FPGA vendor and security framework

fpga-tool attest --device-id FPGA-001 --challenge $(openssl rand -hex 32)

Returns signed attestation report including configuration hash

Continuous attestation mechanisms provide real-time monitoring of FPGA integrity by periodically re-measuring device configurations and alerting on discrepancies. This approach is particularly valuable for detecting dynamic attacks that attempt to modify FPGA behavior after initial deployment.

Differential attestation compares the configuration of multiple identical FPGA devices to identify outliers that may indicate compromise. By establishing baselines from known-good devices and continuously monitoring for deviations, organizations can detect subtle alterations that might escape other detection methods.

Zero-knowledge attestation techniques enable verification of FPGA integrity without revealing sensitive configuration details. This is particularly important for protecting intellectual property while still maintaining security oversight. Advanced cryptographic protocols allow devices to prove compliance with security policies without disclosing proprietary design information.

Supply chain attestation extends the verification process to cover the entire lifecycle of FPGA deployments. From manufacturing through distribution to final installation, each stage can generate attestation evidence that contributes to overall trust assessment. Blockchain-based solutions are emerging to provide immutable records of FPGA provenance and configuration history.

Integration with existing security information and event management (SIEM) systems allows attestation data to contribute to broader security monitoring efforts. Correlating FPGA integrity measurements with network traffic patterns, system logs, and other security telemetry provides comprehensive visibility into potential threats.

However, implementing effective hardware attestation requires addressing several technical challenges. Ensuring that measurement processes themselves cannot be subverted demands careful design of secure boot sequences and protected execution environments. Managing cryptographic keys across large fleets of FPGA devices introduces complexity in key distribution and rotation procedures.

Despite these challenges, hardware attestation offers unparalleled assurance for FPGA security. When properly implemented, it provides mathematical proof of device integrity that is far more reliable than traditional software-based verification methods.

Key Insight: Hardware attestation transforms FPGA security from reactive detection to proactive prevention by providing cryptographic guarantees of device integrity throughout the system lifecycle.

What Role Does Supply Chain Security Play in Preventing FPGA Compromises?

Supply chain security emerges as a foundational element in defending against FPGA-based threats, given that many attacks originate during the manufacturing, distribution, or initial configuration phases of these devices. The distributed nature of FPGA production—with design, fabrication, and assembly often occurring in separate facilities—creates numerous opportunities for adversaries to introduce malicious modifications.

The first line of defense involves thorough vetting of FPGA suppliers and their subcontractors. Organizations should conduct comprehensive risk assessments of all entities involved in the FPGA supply chain, evaluating their security practices, geographic locations, and potential exposure to nation-state influences. This due diligence extends beyond initial vendor selection to include ongoing monitoring of supplier security posture and incident response capabilities.

Component authentication mechanisms help ensure that FPGA devices received match those ordered from legitimate sources. This includes verifying serial numbers, lot codes, and cryptographic certificates embedded in devices during manufacturing. Automated verification systems can flag discrepancies that may indicate counterfeit or tampered products.

{ "supply_chain_verification": { "device_serial": "XC7A100T-FTG256-2", "lot_number": "L202604", "manufacturing_date": "2026-03-15", "certificate_chain": [ "manufacturer_cert.pem", "distributor_cert.pem", "integrator_cert.pem" ], "verification_status": "verified", "tamper_indicators": [] } }

Secure transportation protocols protect FPGA devices during transit from manufacturers to end users. This includes using tamper-evident packaging, GPS tracking, and environmental monitoring to detect unauthorized access or handling. Insurance policies should cover supply chain risks, providing financial recourse in case of compromise.

Configuration management practices govern how FPGA bitstreams are developed, tested, and deployed. Version control systems should track all changes to bitstream files, with mandatory code reviews and security testing before production deployment. Cryptographic signing of all releases prevents unauthorized modifications from being loaded onto devices.

Third-party component integration introduces additional supply chain risks that must be carefully managed. Open-source FPGA cores, third-party IP blocks, and external libraries may contain vulnerabilities or backdoors that could compromise entire systems. Rigorous vetting and testing of all external components is essential before incorporation into production designs.

Manufacturing oversight programs provide visibility into FPGA production processes, helping organizations verify that devices are manufactured according to specified requirements. This may involve on-site audits of fabrication facilities, review of quality control procedures, and participation in industry-wide security initiatives.

Documentation and traceability requirements ensure that complete records exist for every FPGA device deployed in production environments. This includes tracking the origin of all components, recording all configuration changes, and maintaining audit trails that can support forensic investigations if compromises are discovered.

Emergency response procedures address situations where supply chain compromises are detected after deployment. This includes protocols for immediate isolation of affected devices, forensic preservation of evidence, and coordination with law enforcement and regulatory agencies. Communication strategies should inform stakeholders about potential impacts while avoiding panic or misinformation.

Industry collaboration plays a crucial role in strengthening FPGA supply chain security. Information sharing initiatives allow organizations to learn from others' experiences, coordinate responses to emerging threats, and develop common standards for secure FPGA deployment. Participation in sector-specific working groups helps align security practices with regulatory requirements and best practices.

Investment in supply chain security technologies continues to evolve, with new solutions emerging to address specific vulnerabilities. Blockchain-based provenance tracking, artificial intelligence for anomaly detection, and quantum-resistant cryptography represent just a few areas where innovation is driving improved FPGA security outcomes.

Ultimately, supply chain security for FPGAs requires a holistic approach that considers risks at every stage of the device lifecycle. Organizations that prioritize supply chain integrity will be better positioned to defend against sophisticated adversaries who view hardware-level compromises as high-value strategic assets.

Key Insight: FPGA supply chain security demands comprehensive risk management spanning procurement, transportation, manufacturing oversight, and continuous monitoring to prevent pre-deployment compromises.

How Can AI-Assisted Analysis Improve FPGA Security Research?

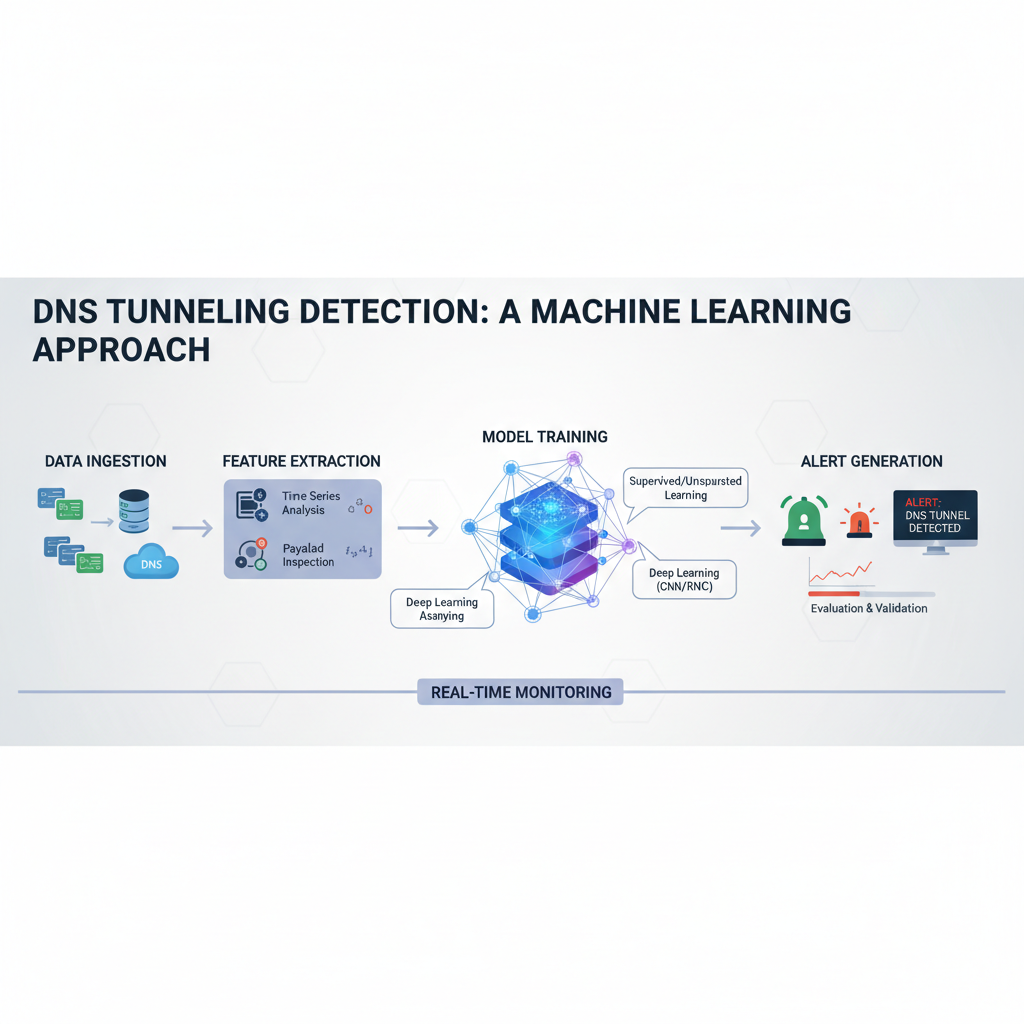

Artificial intelligence and machine learning technologies are revolutionizing FPGA security research by enabling analysis capabilities that would be impossible to achieve through manual methods alone. As FPGA-based threats become increasingly sophisticated, security researchers must leverage AI-powered tools to keep pace with evolving attack techniques and identify subtle indicators of compromise.

Pattern recognition algorithms excel at identifying anomalous behaviors in FPGA configurations that might escape human analysts. By training machine learning models on large datasets of both legitimate and malicious bitstreams, researchers can develop classifiers that automatically flag suspicious design elements. These models can detect subtle statistical deviations in logic utilization, routing patterns, or timing characteristics that suggest malicious intent.

python from sklearn.ensemble import IsolationForest from sklearn.preprocessing import StandardScaler import numpy as np

class FPGAAnomalyDetector: def init(self): self.scaler = StandardScaler() self.model = IsolationForest(contamination=0.1, random_state=42)

def extract_features(self, bitstream_file): # Extract statistical features from FPGA bitstream with open(bitstream_file, 'rb') as f: data = np.frombuffer(f.read(), dtype=np.uint8)

features = [ np.mean(data), np.std(data), np.percentile(data, 25), np.percentile(data, 75), len([x for x in data if x > 200]) / len(data) # High byte ratio ] return np.array(features).reshape(1, -1)def train(self, normal_bitstreams): features = [self.extract_features(bs)[0] for bs in normal_bitstreams] scaled_features = self.scaler.fit_transform(features) self.model.fit(scaled_features)def predict(self, bitstream_file): features = self.extract_features(bitstream_file) scaled_features = self.scaler.transform(features) return self.model.predict(scaled_features)[0]Natural language processing techniques assist researchers in analyzing documentation, forum posts, and technical papers related to FPGA security. AI models can identify emerging threat trends, correlate findings across disparate sources, and highlight potential vulnerabilities before they're exploited in the wild. This proactive approach enables security teams to prepare defenses ahead of actual attacks.

Generative AI tools accelerate the development of FPGA security testing frameworks by automatically generating test cases, creating synthetic bitstreams for benchmarking, and proposing novel detection algorithms. Researchers can iterate more quickly on security hypotheses, validating ideas through simulation and emulation environments powered by AI-driven optimization.

Predictive analytics models forecast potential attack vectors based on historical data and current threat intelligence. By analyzing patterns in reported FPGA compromises, AI systems can identify industries, device types, or geographic regions most likely to be targeted next, allowing organizations to prioritize their defensive investments accordingly.

Automated reverse engineering capabilities help security researchers understand complex FPGA designs more efficiently. AI-assisted decompilation tools can reconstruct high-level representations of bitstream logic, making it easier to identify malicious components within large, intricate designs that would be overwhelming to analyze manually.

Collaborative AI platforms enable security researchers worldwide to share insights and coordinate responses to emerging FPGA threats. These systems can automatically synthesize findings from multiple sources, identify conflicting reports, and highlight consensus opinions that guide community response efforts.

mr7.ai provides specialized AI tools designed specifically for FPGA security research. Their suite includes KaliGPT for penetration testing assistance, 0Day Coder for exploit development, and DarkGPT for advanced threat analysis. New users receive 10,000 free tokens to experiment with these cutting-edge capabilities.

The mr7 Agent represents a breakthrough in automated FPGA security assessment. Running locally on researchers' machines, this AI-powered platform can perform comprehensive vulnerability scans, generate detailed reports, and recommend remediation strategies without requiring cloud connectivity. Its integration with popular FPGA development tools streamlines the research workflow while maintaining data privacy.

Deep learning architectures show promise for detecting sophisticated FPGA rootkits that employ evasion techniques to avoid traditional detection methods. Convolutional neural networks can identify visual patterns in bitstream representations, while recurrent networks can detect temporal anomalies in device behavior that suggest malicious activity.

However, AI adoption in FPGA security research faces several challenges. The lack of publicly available datasets limits training opportunities for machine learning models, while the proprietary nature of many FPGA designs creates barriers to collaborative research. Addressing these issues requires industry cooperation and investment in open research initiatives.

Despite these obstacles, AI-assisted analysis is becoming indispensable for FPGA security professionals. Organizations that embrace these technologies will gain significant advantages in detecting and responding to hardware-level threats that traditional security approaches cannot adequately address.

Key Insight: AI-powered analysis tools dramatically enhance FPGA security research capabilities, enabling faster threat detection, automated reverse engineering, and predictive modeling of emerging attack patterns.

Key Takeaways

• FPGA rootkits represent a fundamental shift in cyber threats, operating at the hardware logic level to achieve unprecedented persistence and stealth • Unlike traditional firmware implants, FPGA-based malware executes directly in configurable hardware, making detection and removal extremely challenging • Hardware attestation using cryptographic proofs provides the most reliable method for verifying FPGA integrity and preventing unauthorized modifications • Supply chain security is critical for FPGA defense, requiring comprehensive risk management from procurement through deployment and maintenance • AI-assisted analysis tools significantly enhance FPGA security research capabilities, enabling pattern recognition, automated reverse engineering, and predictive threat modeling • Defense strategies must integrate physical security measures, network segmentation, continuous monitoring, and specialized incident response procedures • Organizations should leverage platforms like mr7.ai to access cutting-edge AI tools for FPGA security assessment and threat analysis

Frequently Asked Questions

Q: What is an FPGA rootkit and how does it differ from traditional malware?

An FPGA rootkit is malicious logic programmed directly into a Field-Programmable Gate Array's configuration memory, operating at the hardware level rather than as software code. Unlike traditional malware that runs on processors, FPGA rootkits execute as custom digital circuits within the chip itself, making them persistent across reboots and resistant to software-based removal techniques.

Q: How can organizations detect FPGA-based compromises in their networks?

Organizations can detect FPGA compromises through hardware attestation, power analysis monitoring, behavioral anomaly detection, and supply chain verification. This includes implementing cryptographic verification of bitstream integrity, deploying sensors to monitor electromagnetic emissions, and conducting regular physical inspections of critical infrastructure devices for signs of tampering.

Q: What are the main challenges in removing FPGA rootkits once detected?

Removing FPGA rootkits is challenging because they're physically programmed into the chip's configuration memory, requiring complete bitstream replacement rather than simple software uninstallation. Recovery may necessitate device replacement if the rootkit has modified critical hardware functions or if secure erase procedures aren't available for the specific FPGA model.

Q: How do attackers typically gain access to FPGA devices for rootkit installation?

Attackers commonly gain FPGA access through supply chain compromises during manufacturing or distribution, exploiting software vulnerabilities in configuration interfaces, or achieving physical access to devices for direct programming. They may also intercept and modify bitstream files during legitimate update procedures or target weak authentication mechanisms in FPGA management systems.

Q: What preventive measures can protect against FPGA rootkit deployment?

Preventive measures include implementing secure supply chain practices, enforcing cryptographic signing of all FPGA bitstreams, deploying hardware attestation mechanisms, segmenting FPGA-equipped devices on isolated network segments, and maintaining strict physical security controls over critical infrastructure. Regular security audits and continuous monitoring for anomalous behavior also help prevent successful compromises.

Try AI-Powered Security Tools

Join thousands of security researchers using mr7.ai. Get instant access to KaliGPT, DarkGPT, OnionGPT, and the powerful mr7 Agent for automated pentesting.